Internal Report #62 T. L. Garrard September 18, 1975

### MJS-CRS BCE\_HARDWARE\_DESCRIPTION

- 1. General Description

- A. Introduction

- B. Objectives

- C. General Description of Hardware

D. General Description of Software

- II. Interface Hardware

- A. FDS Simulator and Control Unit

- B. Calibration Mode Stimulus Module

- C. Functional Test Mode Stimulus Module

- III. ADPE and ADPE Interfaces

- IV. Figures

- V. Tables of Signals

### I.A.1

### I. General Description

A. Introduction

This plan describes the BCE (bench checkout equipment) for the CRS (cosmic-ray subsystem) to be flown on MJS (Mariner-Jupiter-Saturn). The BCE consists of computer-controlled hardware which will control and support the CRS when it is off the spacecraft. The BCE description may be broken down into three categories:

1) the interface hardware, which will be constructed at Caltech.

2) the computer hardware, or ADPE (automatic data processing equipment).

3) the software or programming.

Since the ADPE and software are described elsewhere, this plan is primarily concerned with a description of the interface hardware.

### I.B.1

#### B. Objectives

The objectives of the BCE may be grouped under four main headings:

1) Acquire and accumulate data from an externally stimulated CRS.

2) Acquire, accumulate, and monitor analog status data.

3) Calibrate PHA's and discriminator thresholds.

4) Perform functional tests of the CRS logic implementation.

Mode 1, acquire and accumulate, is intended to allow the BCE to support calibrations of the CRS with particle beams at accelerator facilities, with radioactive sources, and with ground level muons. In this mode the ADPE sends commands to the CRS, issues word gates, etc. as necessary to read out events, records data on mag tape, and types a summary of the data to the operator.

Mode 2, monitor status, will be active at all times. The ADPE will read analog status data, power supply voltage and current, and temperature probes and will check the value of these parameters. Any significant departures from normal status will cause warnings to be typed and, if warranted, CRS power may be cut off.

Mode 3, calibrate, and mode 4, test, are <u>mutually exclusive</u> since they share the same hardware. In calibrate mode test pulses are connected to the test input of one of the CRS preamps and the appropriate rate scaler or PHA buffer is read out. This process requires that the BCE be able to set the CRS rate multiplexor (mux) to the appropriate rate scaler in a reasonably short time.

In test mode, the ADPE generates events according to a programmed sequence (possibly involving a psuedo-random number generator). The appropriate preamps are triggered and the CRS rate and PHA data are read out and compared with expected response. Deviations are noted for further investigation. C. General Description of Hardware

The hardware consists of the ADPE and the interface hardware. The interface hardware may be broken down into three modules:

The Flight Data System(FDS) simulator and control unit, called the FDC.

2) The calibration mode stimulus module, called the Cal Stim.

3) The functional test mode stimulus module, called the FT Stim.

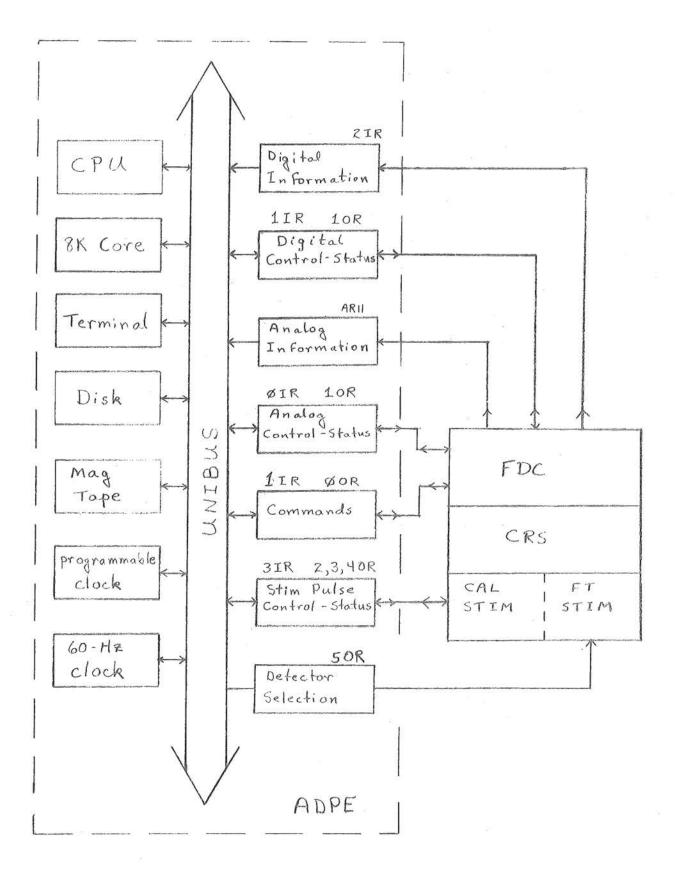

The breakdown of the BCE hardware into these categories is illustrated in Figure 1.

A brief overall description of the BCE hardware is presented here; a more detailed description of each of the hardware categories is given in following sections.

The FDC will, under ADPE control, generate and receive most of the CRS/FDS signals. These signals are tabulated in Table 1. A more complete description is in the FDS memo. Signals received from the CRS will be formatted and sent to the ADPE. The FDC will also control the state of the CRS rate multiplexor and the CRS power.

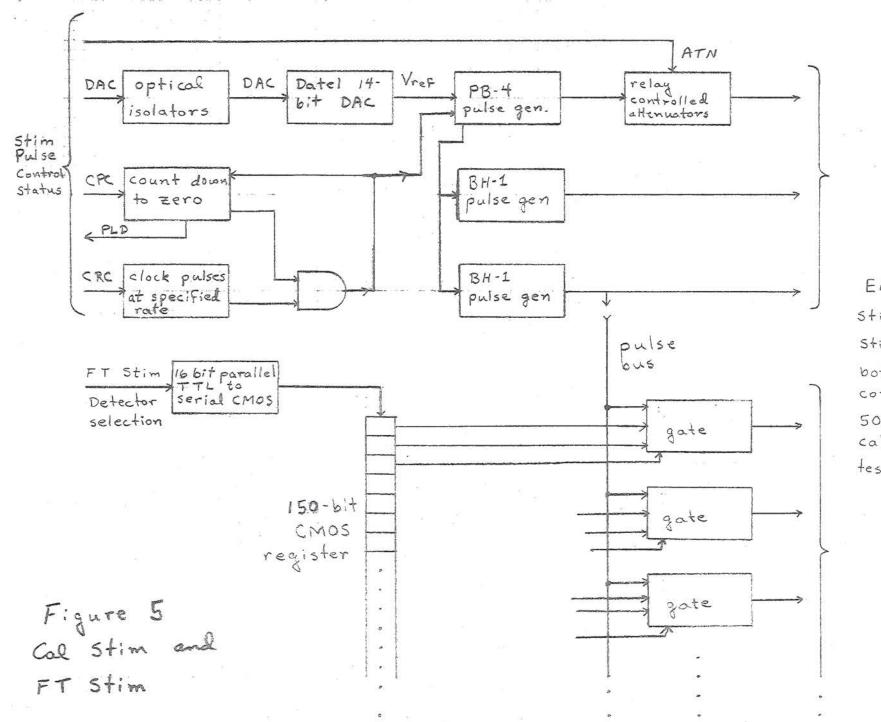

The Cal Stim will generate a precision analog test pulse which will be manually connected to the appropriate CRS preamp test input. The rate and amplitude of this pulse is under ADPE control. In addition two coincident pulses with fixed amplitude are generated and used if necessary to satisfy CRS logic requirements for particular rate scalers or PHA buffers.

The FT Stim module will generate up to 50 independent pulses at the 50 CRS preamp test inputs. These pulses have up to 3 possible amplitude states (or four states if zero amplitude is counted). The FT Stim shares

the pulse rate control unit of the Cal Stim. In addition, the same 50 ohm coax lines are used to connect either the Cal Stim or the FT Stim to the CRS test inputs.

### D. General Description of Software

The software will be programmed in the FORTH language. Appropriate vocabulary for the four modes of operation specified in section I.B. will be provided. The high-level language features of FORTH should allow easy modification of extension of software when unforeseen situations arise.

#### II.A.1.

#### II. Interface Hardware

A. FDS Simulator and Control Unit

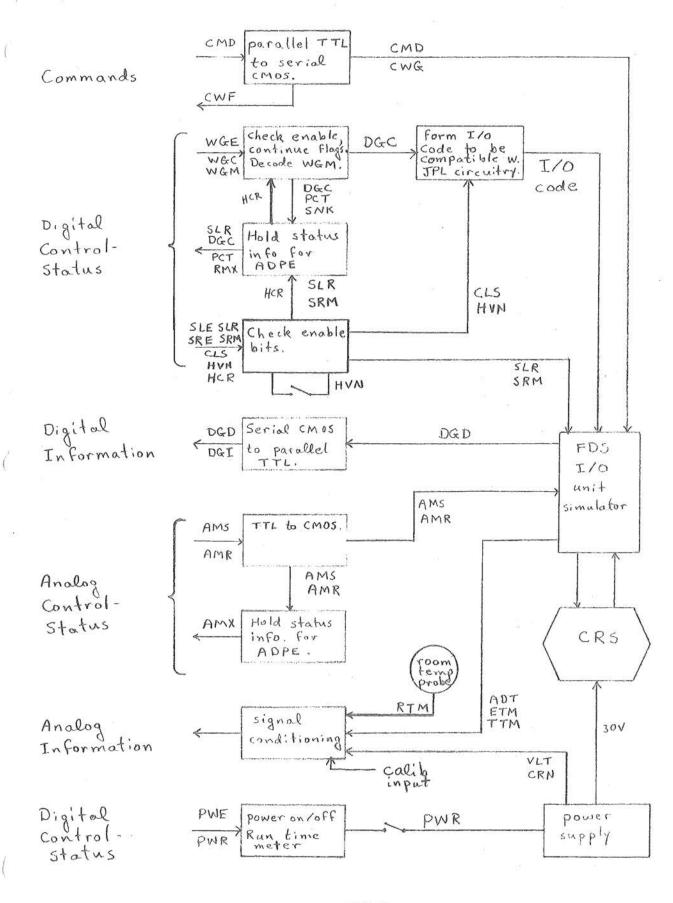

The FDC is illustrated in Figure 2. It supports all functions of the FDS. It also controls CRS power, controls the state of the rate multiplexor, and includes registers which duplicate the state of the CRS multiplexors. Signal conditioning of analog signals is done in the FDC.

As seen in Figure 2, the FDC can be broken down into several submodules which are logically more-or-less separate. These will be described at this point.

The command sub-module receives a 12-bit parallel command word from the ADPE. It generates a command word gate (CWG) and feeds the command to the CRS in serial fashion. A signal (CWF) is also sent to the ADPE to acknowledge receipt and transmission of the command.

The digital information sub-module receives serial digital data from the CRS and converts the date to parallel for the ADPE.

Word gates, redundancy selection, various discrete commands, and power on/off control are handled by the digital control-status hardware. This hardware includes a register which may be read by the ADPE at any time to determine what type of data was most recently received by the digital information submodule, i.e., whether it was status, rate, or pulse-height data, which of the 4 pulse-height words it was, whether it was read through the A or B redundant lines, and what the state of the rate multiplexor is. II.A.2.

Word gates - PWG, RWG, SWG - are generated in one of the eight formats listed in Table 2. The format is selected by the ADPE. Due care must, of course, be taken to satisfy the timing requirements specified in the FDS memo. Note that once the word gate sub-module is placed in one of the eight possible modes, no further interaction with the ADPE is required until the mode is to be changed.

The signals CLS, HVN, SLR, AMS, and AMR are generated with the proper timing by the FDC whenever required by the corresponding signal from the ADPE. The non-FDS signals SRE, SRM, HCR, PWR, and SLE are generated in the same manner.

An analog information sub-module handles the conditioning necessary between the analog to digital converter in the ADPE and the various analog signals of interest which are listed in Table 1.

Note that the signals for which transmission of a zero can cause a change of state must have associated enable bits, e.g., if the three bits that specify the word gate mode are all zero, does that mean change to mode zero, or does it mean no change from current status? This question is settled by the enable bit, which must be on before any change will take place.

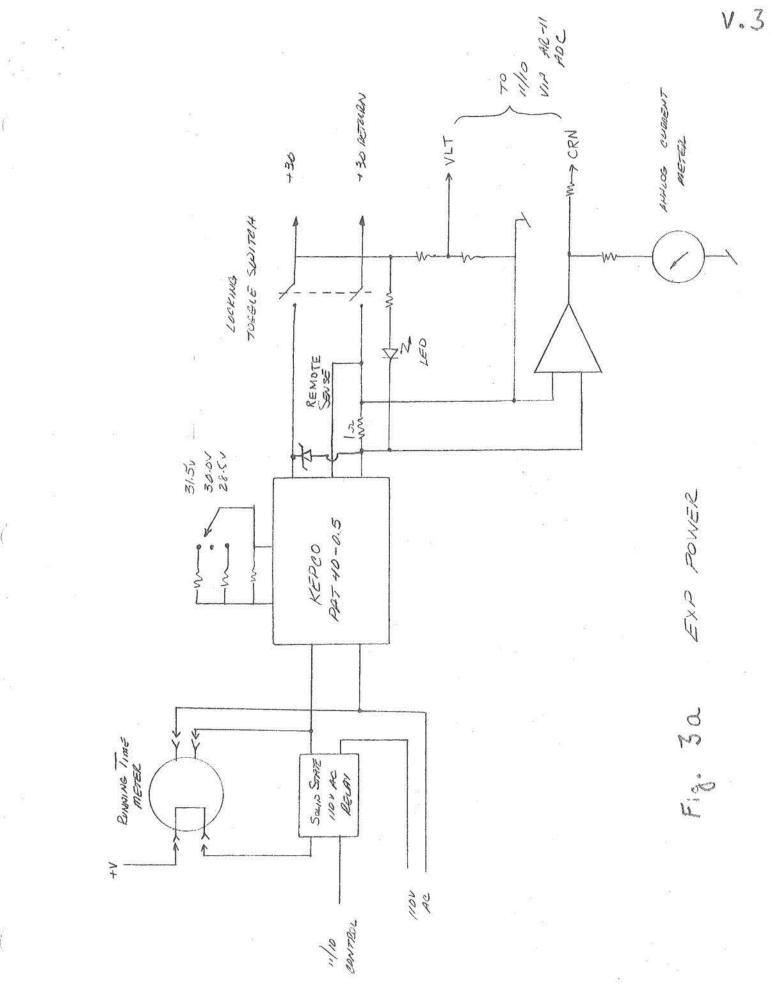

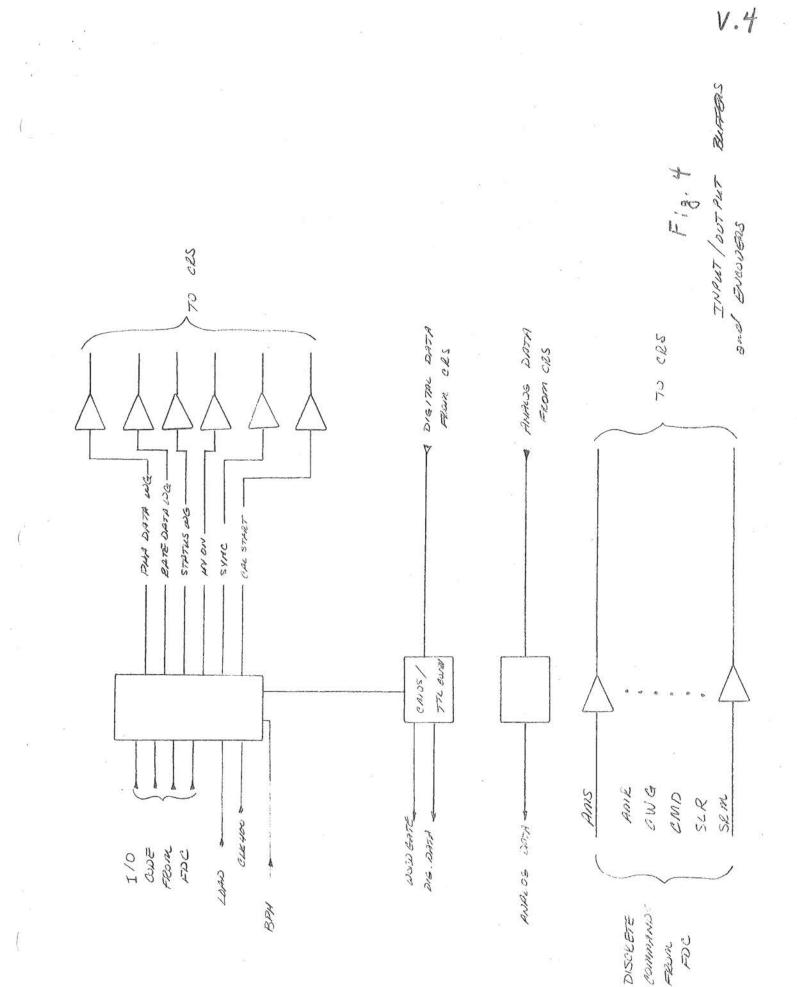

All I/O to the CRS except power is through an I/O unit copied from the JPL FDS I/O unit specifications. Figures3 and 4 give details of the power system and the I/O unit.

### II.A.3

The rate mux in the CRS includes two separate counters-- a 16 state mux which specified which rates are fed to the accumulators and a 30 state mux which specifies which rate buffer is being read out. The 30 - state counter serves some additional functions; when the counter overflows from the 30th state to the first, a pulse is generated which transfers the contents of the rate accumulators to the rate buffers and initiates the 24 - to 12 - bit compression, increments the 16 - state rate mux, and increments the digital status mux.

The SRM signal is used to freeze the 16 - state rate mux, but the 30 state mux must be allowed to increment normally with each RWG so that the transfer and compression will take place. The possibility of adding a BCE controlled signal which would cause the transfer was considered and rejected on the basis of possible impact on CRS reliability. II.B.7.

### B. Calibration Mode Stimulus Module

The Cal Stim is schematically illustrated in Figure 5. The pulse generated for calibration is controlled in amplitude by a 14-bit DAC used as a reference voltage by the pulse generator and a 4-bit, ADPE-controlled attenuator. The dynamic range necessary for discriminator thresholds and PHA ranges is listed in Table 6, which gives threshold and full scale energies, and selected calibration pulses, together with the corresponding voltages needed at the test inputs. Values of the feedback test capacitors are also listed. Absolute accuracy of the calibration should be better than 1% with a goal of 0.3%; repeatability should be better than 0.2% with a goal of 0.05%. In addition to the calibration pulses, two (possibly more) pulses are generated to be used in satisfying CRS coincidence requirements when necessary. ADPE control of the amplitude of these signals is not provided. These signals will normally have constant, fixed amplitude since they are added to the calibration pulse by the CRS slant-discriminator circuitry. The operator can assume manual

control over the amplitude of these signals.

For an example of the normal use of the two fixed amplitude pulses, consider the calibration of the LET I slant discriminator. The calibration pulse would be put into the L1 preamp. The two coincidence pulses would be put into L2 and L3. Thus an L1 L2 L3 coincidence is generated and if the calibration signal is high enough the slant will be triggered and the event will be counted by the R18 rate scaler. The actual threshold of the slant is calculated from the amplitudes of the three signals, not from any one.

The Cal Stim module sends a specified number of pulses at a specified rate under ADPE control. After this number of pulses is sent the ADPE is signalled (by PLD) to read out the necessary data from the CRS.

### II.B.2

The DAC has a sign bit (30R14) in addition to the 14 amplitude bits; it must always be set (1). The 4 attenuator bits control 3 factor-of-eight dividers and 1 factor-of-four dividers as noted below

| Bit No. | Att. factor |

|---------|-------------|

| 40RØ    | 8           |

| 40R1    | 8           |

| 40R2    | 8           |

| 40R3    | 4           |

The pulse rate control uses 2 bits (CRC) to select one of four possible rates:

| CRC | Rate               |

|-----|--------------------|

| 00  | 14400/8 = 1800 cps |

| 01  | 14400/15 = 960 cps |

| 10  | 14400/33 = 436 cps |

| 11  | 14400/191 = 75 cps |

### C. Functional Test Mode Stimulus Module

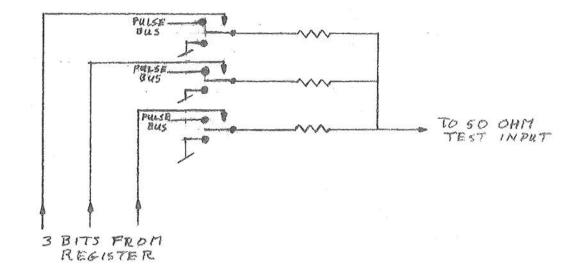

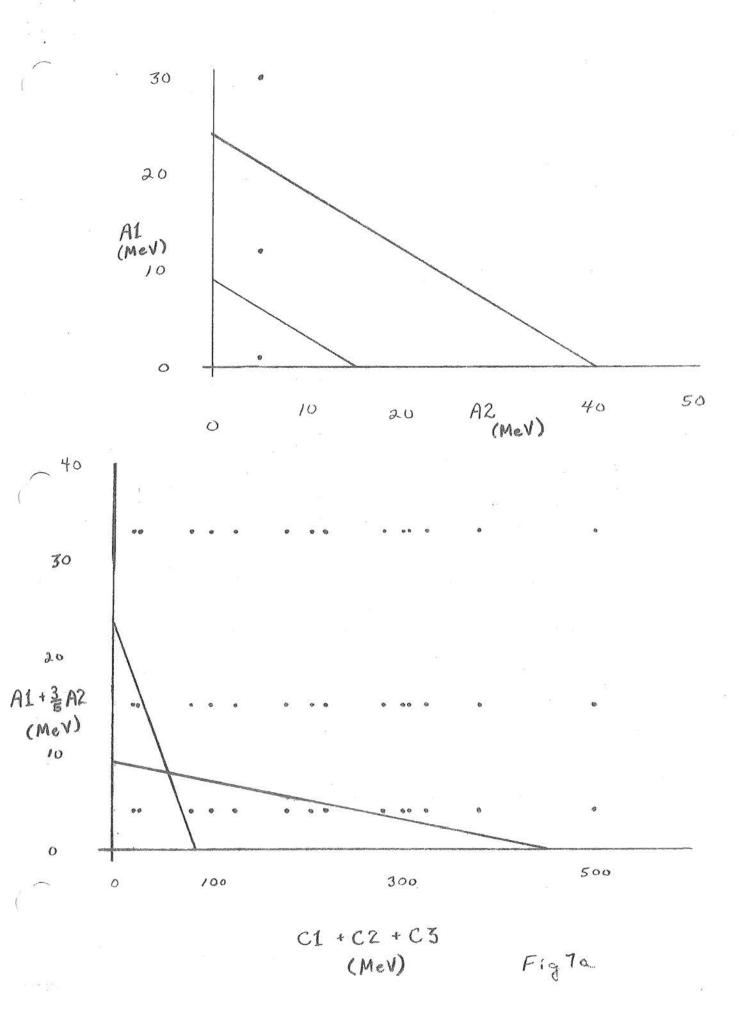

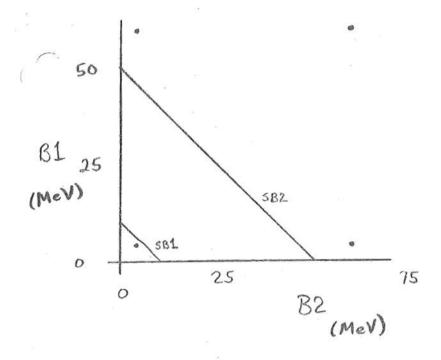

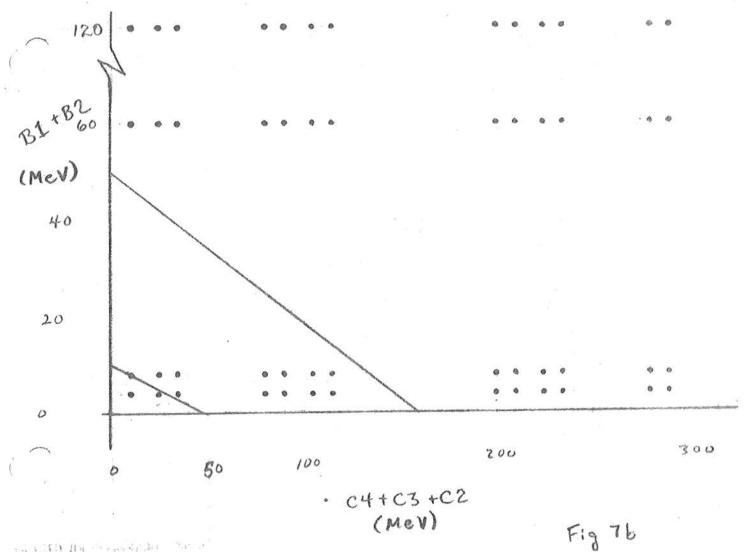

The FT Stim is illustrated in Figure 5. Fifty gates are connected between a pulse bus and the fifty preamp test inputs. Each of the fifty gates may be independently controlled. The gates provide the ADPE with some control over pulse amplitude. Table 3 lists the possible states of each gate. Figure 6 shows details of a gate. Figures 7a and 7b show locations on the 2-D plots which can be pulsed by the FT Stim. Drifts in these locations of up to 5-10% can be tolerated.

Note that the gates actually have other, non-independent states.

Control of the gates is effected through a 150-bit register that may be filled serially with 10 16-bit words from the APDE. The 10 least significant bits of the first of these 10 words are shifted of the end of the register. Table 3 gives the correspondence between bits and states of the gates. After completion of pulses as specified in number and rate by the control, the FT Stim returns a signal to the APDE to read out the necessary data from the CRS.

### III. ADPE and ADPE Interfaces

The ADPE (See Figure 1) consists of a PDP-11/10 computer with the following peripherals:

DEC core memory - 8K words.

TI KSR-733 terminal.

LSi ADM-1 CRT terminal

AED 2500 floppy disk system.

Kennedy 9700 mag tape system.

DEC AR-11 analog subsystem

DEC KW-11 L 60-Hz clock.

2 DECkit 11H parallel digital interfaces.

The TI terminal consists of a keyboard and a 30 character-per-second thermal printer. It uses special, 8 1/2" wide paper. The unit is quiet, light-weight, and portable.

The terminal will be used to display large amounts of rapidly changing data, such as the rate block. It may also be used to display status and for warnings. The display will show 24 80-character lines. A printer interface will be added to allow use of the GSFC Versatec printer for hard copy.

The AED floppy disk has a capacity of 128K words, a maximum transfer rate of 15,625 words/sec, and a maximum access time less than 650 m sec.

The Kennedy tape system uses 600 foot reels of mag tape. It is a single drive system with a drive that requires only 8 3/4" of rack space and that weighs less than 40 pounds.

The 60-Hertz clock generates interrupts 60 times per second if enabled.

The DECkit interfaces are parallel 16-bit interfaces. Each of the two kits has four 16-bit output registers and four 16-bit input receivers.

#### III.1.

An interrupt may be generated by the external device on the input lines. The output, but not the input, words are buffered with flip-flop registers. Table 4 shows the tenative allocations of the interface lines.

The AR-11 analog subsystem includes a 16-channel, 10-bit ADC, a programmable real-time clock and 2 DAC's. It will be used to measure the analog voltages (power supply, thermistors, analog data) provided by the FDC and CRS. The real-time clock is used to generate interrupts after computer-controlled periods ranging from ~ 10  $\mu$  sec to 2.56 sec.

Figure L. ECE System Block Diagram

V.1

V.2

Figure 2. FDC

V. 36

control relay

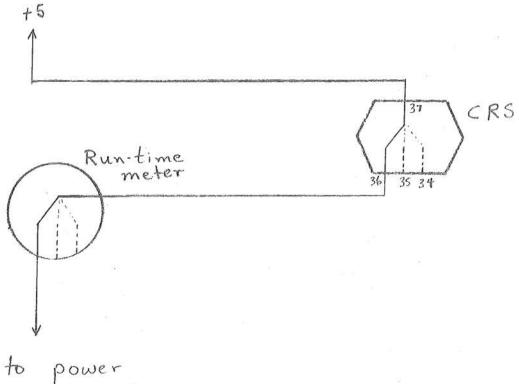

Figure 36. Keying of run-time meter to instrument. PTM is shown.

Either Cal stim or FT stim but not both is connected to 50 line coax cable to CRS test in puts.

V. 5

Figure 6. Details of FT Stim gates

٧.7

$(x_{i+1},y_{i+1},y_{i+1}),\lambda \in$ 14 F E H H H

### VIII. Tables of Signals

This section lists relevant signals in several formats. Table 1 lists signals in logical groupings and specifies which hardware modules are connected to each. Table 2 is a breakdown of the various word gate modes, set by the WGM signal. Table 3 lists the signals used to specify FT Stim states. Table 4 lists the connections to the DECkits. Table 5 lists signals by alphabetical order of mnemonic or acronym.

The notation used for DECkit connections follows:

The input registers are numbered  $\emptyset$ IR through 71R, the output registers are number  $\emptyset$ OR through 70R. Bits are numbered  $\emptyset$  through 15 with the interrupt line on the input registers labelled as bit 16. Thus the first bit on the second output register is 10R $\emptyset$ . Numeral zeros are slashed to avoid confusion.

8 8

35

| Signals                           | Mnemonic   | ADPE interface                                     |

|-----------------------------------|------------|----------------------------------------------------|

| FDS to CRS                        |            |                                                    |

| Command Word Gate                 | CWG        |                                                    |

| Command Word                      | CMD        | $\phi$ or $\langle \phi: 11 \rangle$               |

| Analog Mux Step                   | AMS        | 10R11                                              |

| Analog Mux Reset                  | AMR        | 10R12                                              |

| PHA Data Word Gate A              | PGA        | 14                                                 |

| PHA Data Word Gate B              | PGB        |                                                    |

| Rate Data Word Gate A             | RGA        | di.                                                |

| Rate Data Word Gate B             | RGB        | ×                                                  |

| Status Word Gate                  | SWG        |                                                    |

| Synch                             | SNK        |                                                    |

| Cal Start                         | CLS        | 10R9                                               |

| Redundancy Select                 | SLR        | 10R6                                               |

| HV On                             | HVN        | lor1Ø                                              |

| A Phase Clock                     | APH        | AR-11 ext.                                         |

| B Phase Clock                     | BPH        | clock. input                                       |

|                                   |            |                                                    |

| CRS to FDS                        |            |                                                    |

| Digital Data A                    | DGA        | $\int DGD = DGA + DGB$                             |

| Digital Data B                    | DGB        | $\int 2 \mathrm{IR} \langle \emptyset; 11 \rangle$ |

| Analog Data                       | ADT        | AR-11 ADCØ                                         |

| Analog Signals                    |            |                                                    |

| Telescope Thermistor              | TTM        | AR-11 ADC1                                         |

| Electronics Thermistor            | ETM        | ADC2                                               |

| Room Temp Probe                   | RTM        | ADC3                                               |

| 28V Power-Voltage                 | VLT        | ADC4                                               |

| 28V Power-Current                 | CRN        | ADC5                                               |

| 2                                 |            |                                                    |

| <u>Cal Stim</u>                   | 210        | 30R (Ø:14)                                         |

| Cal Stim Amplitude                | DAC        | 40R (Ø:3)                                          |

| Attenuator                        | ATN        | 20R (12:13)                                        |

| Rate Control                      | CRC        | 20R (Ø:11)                                         |

| Pulse Count                       | CPC        | ZURQUIT                                            |

| Other                             | 34         |                                                    |

| Power on/off                      | PWR        | 10R14                                              |

| PWR Enable                        | PWE        | 10R13                                              |

| Analog Mux Status                 | AMX        | $\emptyset$ IR $\langle \emptyset: 4 \rangle$      |

| Command Word Flag                 | CWF        | ØIR16                                              |

| SLR Enable                        | SLE        | 10R5                                               |

| Redundancy Select (in)            | SLR        | lirø                                               |

| Word Gate Mode                    | WGM        | $10R\langle 2:4\rangle$                            |

| WGM Enable                        | WGE        | lorø                                               |

| Word Gate Continue                | WGC<br>HCR | 10R1<br>10R15                                      |

| Hardware Clear<br>Rate Mux Status | RMX        | 4IR (Ø: 8)                                         |

| Stop Rate Mux                     | SRM        | 10R8                                               |

| SRM Enable                        | SRE        | 10R7                                               |

| Digital Data Code                 | DGC        | 1IR (1:2)                                          |

| Digital Data Interrupt            | DGI        | 2IR16                                              |

| PWG Count of 4                    | PCT        | 1IR (3:4)                                          |

| Pulsing Done                      | PLD        | 1IR16                                              |

|                                   |            |                                                    |

### Table 2. Word Gate and Digital Data Codes

| WGM | Word Gate Mode            |                                  |

|-----|---------------------------|----------------------------------|

| 0   | 30 Rate                   | rate acq.                        |

| 1   | SNK*16(30 Rate*Status)    | rate or status acq.              |

| 2   | 4 PHA                     |                                  |

| 3   | 1 Rate                    | software mode                    |

| 4   | 1 Status                  |                                  |

| 5.  | 16 (BS Status) 30 (Rate 4 | PHA] at 400 Hz<br>at 5 Hz        |

| 6.  | n n                       | at 5 Hz $\int$ spacectait normal |

| 7.  | SNK                       |                                  |

(BS = Blank or Synch)

DGC Digital Data Code

00 PHA

01 Rate

10 Status

.

1

| Word | Bit                                  | Preamp  | Energy   |

|------|--------------------------------------|---------|----------|

| 1    | 5                                    | H1A1    | 1        |

|      | 4                                    |         | 12       |

|      | 3                                    |         | 30       |

|      | 3<br>2<br>1                          | H1A2    | . 5<br>0 |

|      | 1                                    |         | 0        |

|      | 0                                    |         | 0        |

| 2    | 15                                   | H1B1    | 4        |

|      | 14                                   |         | 60       |

|      | 13                                   |         | 0        |

|      | 12                                   | H1B2    | 4        |

|      | 11                                   |         | 60       |

|      | 10                                   |         | 0        |

|      | 9                                    | H1C1    | 20       |

|      | 8                                    |         | 100      |

|      | 7                                    |         | 200      |

|      | 8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | H1C2    | 80       |

|      | 5                                    |         | 200      |

|      | 4                                    | 111.00  | 0<br>24  |

|      | 3                                    | H1C3    | 200      |

|      | 2                                    |         | 0        |

|      | 0                                    | H1C4    | 10       |

|      | 0                                    |         |          |

| 3    | 15                                   | H1C4    | . 0      |

|      | 14                                   | 0.      | 0        |

|      | 13                                   | H1G1    | 1.5      |

|      | 12                                   |         | 5        |

|      | 11                                   |         | 20       |

|      | 10                                   | H1G2    | 1.5      |

|      | 9                                    |         | 0        |

|      | 8<br>7<br>6<br>5                     |         | 0        |

|      | 7                                    | H1G3    | 1.5      |

|      | 6                                    |         | 0        |

|      |                                      |         | 0        |

|      | 4                                    | H1G4    | 1.5      |

|      | 4<br>3<br>2<br>1<br>0                |         | 0        |

|      | 2                                    | 110 4 1 | 0<br>1   |

|      | I                                    | H2A1    | 12       |

|      | 0                                    |         | 12       |

| 4    | 15                                   | H2A1    | 30       |

|      | 14                                   | H2A2    | 5        |

|      | 13                                   |         | 0        |

|      | 12                                   |         | 0        |

|      | 11                                   | H2B1    | 4        |

|      | 10                                   |         | 60       |

|      |                                      |         | 0        |

|      | 9<br>8<br>7                          | H2B2    | 4        |

|      | 7                                    |         | 60       |

|      | 6                                    |         | 0        |

|      |                                      |         |          |

| Word | Bit                        | Preamp | Energy                |

|------|----------------------------|--------|-----------------------|

|      | 5<br>4<br>3                | H2C1   | 20<br>100<br>200      |

|      | 3<br>2<br>1<br>0           | H2C2   | 80<br>200<br>0        |

| 5    | 15<br>14<br>13             | Н2С3   | 24<br>200<br>0        |

|      | 12<br>11<br>10             | H2C4   | 10<br>0<br>0          |

|      | 9<br>8<br>7                | H2G1   | 1.5<br>5<br>20        |

|      | 6<br>5<br>4                | H2G2   | 1.5<br>0<br>0         |

|      | 5<br>4<br>3<br>2<br>1<br>0 | H2G3   | 1.5<br>0<br>0         |

| 6    | 15                         | H2G4   | 1.5                   |

|      | 14<br>13<br>12<br>11       | LAL1   | 0<br>5<br>24<br>0     |

|      | 10<br>9<br>8               | LAL2   | 5<br>24<br>0          |

|      | 7<br>6<br>5                | LAL3   | 5<br>60               |

|      | 5<br>4<br>3<br>2           | LAL4   | 0<br>5<br>0<br>0<br>5 |

|      | 1<br>0                     | LBL1   | 24                    |

| 7    | 15<br>14<br>13<br>12       | LBL2   | 0<br>5<br>24<br>0     |

|      | 11<br>10                   | LBL3   | 5<br>60               |

|      | 9<br>8<br>7<br>6           | LBL4   | 0<br>5<br>0<br>0      |

(

7

| Word | Bit                                            | Preamp | Energy                      |

|------|------------------------------------------------|--------|-----------------------------|

|      | 5<br>4<br>3                                    | LCL1   | 5<br>24<br>0                |

|      | 5<br>4<br>3<br>2<br>1<br>0                     | LCL2   | 5<br>24<br>0                |

| 8    | 15<br>14                                       | LCL3   | 5 60                        |

|      | 13<br>12<br>11                                 | LCL4   | 0<br>5<br>0<br>0<br>5<br>24 |

|      | 10<br>9<br>8                                   | LDL1   |                             |

|      | 7<br>6<br>5                                    | LDL2   | 0<br>5<br>24                |

|      | 9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | LDL3   | 0<br>5<br>60                |

|      |                                                | LDL4   | 0<br>5                      |

| 9    | 15<br>14<br>13<br>12                           | D1     | 0<br>0<br>1<br>10           |

|      | 11<br>10<br>9<br>8                             | D2     | 0<br>1<br>10<br>0           |

|      | 9<br>8<br>7<br>6<br>5                          | D3     | 1<br>15                     |

| 12   | 4<br>3<br>2<br>1                               | D4     | 0<br>1<br>15<br>0           |

|      | 1<br>0                                         | D5     | 1<br>15                     |

| 10   | 15<br>14<br>13<br>12                           | D6     | 0<br>1<br>15<br>0           |

|      | 11<br>10<br>9                                  | D7     | 0<br>1<br>15<br>0           |

| Bit |

|-----|

| 8   |

| 7   |

| 6   |

| 5   |

| 4   |

| 3   |

| 2   |

| 1   |

| 0   |

| Preamp | Energy                          |

|--------|---------------------------------|

| D8     | 1                               |

|        | 0                               |

|        | 0                               |

| GA     | 1                               |

|        | 0                               |

|        | 0                               |

| GB     | 1                               |

|        | 0                               |

|        | 0                               |

|        | 0<br>0<br>1<br>0<br>0<br>1<br>0 |

|         |            |                                                                                          |                                                                                                  |                                                                                         | φ ::                |

|---------|------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------|

| Ē       | Register   | Bits                                                                                     |                                                                                                  | Use                                                                                     | 9 - 18<br>- 18      |

| Input:  | ØIR        | <Ø:4><br><5:15><br>16                                                                    |                                                                                                  | AMX<br>(unused)<br>CWF                                                                  |                     |

|         | lir        | Ø<br><1:2><br><3:4><br><5:13><br><14:15>                                                 |                                                                                                  | SLR<br>DGC<br>PCT<br>RMX                                                                |                     |

|         | 2IR        | $\langle 14:15 \rangle$<br>16<br>$\langle 0:11 \rangle$<br>$\langle 12:15 \rangle$<br>16 | 20                                                                                               | (unused)<br>PLD<br>DC = DGA<br>(unused)<br>DGI                                          | + DGB               |

|         | 3IR        |                                                                                          |                                                                                                  | (unused)                                                                                |                     |

|         | 4IR        |                                                                                          | а<br>а                                                                                           | (unused)                                                                                |                     |

|         | 5IR        |                                                                                          |                                                                                                  | (unused)                                                                                | * # #               |

|         | 6IR        |                                                                                          |                                                                                                  | (unused)                                                                                |                     |

|         | 7IR        |                                                                                          | 18                                                                                               | (unused)                                                                                |                     |

| Output: | ØOR        | <pre> &lt;\$\$:11\$  &lt;12:15\$</pre>                                                   | t. 2                                                                                             | CMD<br>(unused)                                                                         |                     |

| v       | 10R<br>20R | Ø<br>1.<br><2:4><br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br><12:13> | 8<br>8<br>9<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | WGE<br>WGC<br>SLE<br>SLR<br>SRE<br>SRM<br>CLS<br>HVN<br>AMS<br>AMR<br>PWE<br>PWR<br>HCR |                     |

|         | 30R        | (0:11)                                                                                   | (se                                                                                              | CRC CPC                                                                                 | Cal Stim            |

| ٤,      | 40R        | <p:14></p:14>                                                                            |                                                                                                  | DAC<br>ATN                                                                              | Contract D Weightet |

| J.,     | 50R        | <ø:15>                                                                                   |                                                                                                  | FT Stim                                                                                 | 9<br>19             |

|         |            |                                                                                          |                                                                                                  |                                                                                         |                     |

|         | 60R        |                                                                                          |                                                                                                  | (unused)                                                                                |                     |

|         | 70R        |                                                                                          |                                                                                                  | (unused)                                                                                |                     |

## TABLE 5

## ALPHABETICAL LIST OF SIGNAL MNEMONICS

| NAME                                          | SIGNAL                                                                                                                      | COMMENTS                                                                                                                             |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ADT<br>AMR<br>AMS<br>AMX<br>APH<br>ATN        | Analog Data<br>Analog Mux Reset<br>Analog Mux Step<br>Analog Mux Status<br>A Phase Clock<br>Cal Stim Attenuator             | from CRS<br>to CRS<br>to CRS<br>FDC register for ADPE to read                                                                        |

| BPH                                           | B Phase Clock                                                                                                               | *                                                                                                                                    |

| CLS<br>CMD<br>CPC<br>CRC<br>CRN<br>CWF<br>CWG | Cal Start<br>Command<br>Cal Stim Pulse Count<br>Cal Stim Rate Control<br>Current<br>Command Word Flag<br>Command Word Gate  | to CRS<br>to CRS<br>no of pulses to be output<br>rate of pulsing<br>current on 30V line to CRS<br>means command was issued<br>to CRS |

| DAC<br>DGA<br>DGB<br>DGC<br>DGD<br>DGI        | Cal Stim Pulse Amplitude<br>Digital Data A<br>Digital Data B<br>Digital Date Code<br>Digital Data<br>Digital Data Interrupt | from CRS<br>from CRS<br>see table 2<br>DGA + DGB<br>Says data is available                                                           |

| ETM                                           | Electronics Temperature                                                                                                     | from CRS                                                                                                                             |

| HCR<br>HVN                                    | Hardware Clear<br>High Voltage On                                                                                           | Clears registers in digital<br>control-status, etc.<br>to CRS. Must be switch enabled.                                               |

| PCT<br>PLD<br>PWE<br>PWR                      | PWG Count of 4<br>Pulsing Done<br>PWR Enable<br>Power On/Off                                                                | from Stim to ADPE<br>gates PWR from ADPE to relay<br>Requires PWE and switch enable                                                  |

| RMX<br>RTM                                    | Rate Mux Status<br>Room Temperature                                                                                         | FDC register for ADPE to read                                                                                                        |

| SLE<br>SLR<br>SNK<br>SRE<br>SRM               | SLR Enable<br>Redundancy Select<br>Synch<br>SRM Enable<br>Stop Rate Mux                                                     | to CRS<br>to CRS                                                                                                                     |

VI.10.

# TABLE 5 cont'd

6

| TTM        | Telescope Temperature            | from CRS                                 |

|------------|----------------------------------|------------------------------------------|

| VLT        | Voltage                          | on 30V line to CRS                       |

| WGC<br>WGE | Word Gate Continue<br>WGM Enable | repeat word gate pattern                 |

| WGM        | Word Gate Mode                   | specifies which pattern.<br>See Table 2. |